Kombinační LO jsou takové, u kterých stavy na výstupech závisí pouze na okamžitých kombinacích stavů jejich vstupů. U kombinačních logických obvodů se závislost výstupních

funkčních hodnot na hodnotách vstupních proměnných popisuje pravdivostní tabulkou nebo pomocí logických výrazů. Pro realizaci lze použít základních logických členů (NAND,

AND, NOR, OR).

Některé důležité logické funkce: INV, AND, OR, EXOR, EXNOR

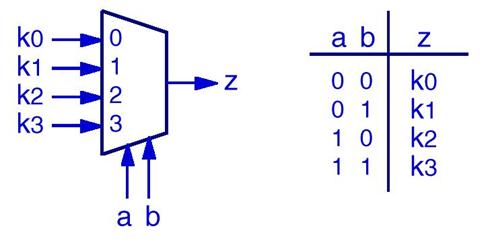

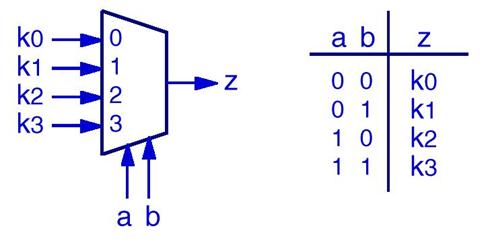

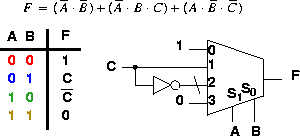

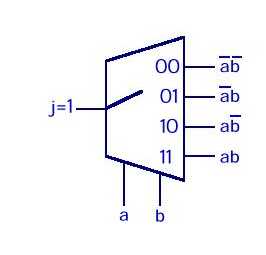

Multiplexor je kombinační číslicový obvod, který má 2n vstupů a jeden výstup. Hodnota vstupu daného adresou (na obr. vstupy a, b) je přenesena na výstup multiplexoru. Používá se k výběru dat nebo generování logických funkcí. Také se používá pro kódu sériového z kódu paralelního. Jako integrovaný obvod se vyrábí jako např. 74150 nebo 74151 nebo CMOS 4051 - 4053 (přepínatelné multiplexor/demultiplexor).

Příklad generování funkce pomocí multiplexoru

Demultiplexor je kombinační číslicový obvod, který má 2n výstupů a jeden vstup. Do výstupu daného adresou (na obr. vstupy a, b) je přenesena hodnota vstupu. Jedná se o opak multiplexoru. Jako integrovaný obvod se vyrábí jako např. 74137 nebo 74138 nebo CMOS 4051 - 4053 (přepínatelné multiplexor/demultiplexor).

Mají tu vlastnost, že jejich výstupní proměnné jsou uřčeny nejen kombinací hodnot vstupních proměnných v daném okamžiku, ale i minulými hodnotami některých proměnných. Z toho vyplývá, že si sekvenční obvod musí pamatovat hodnoty z předcházejícího stavu, což znamená, že musí obsahovat paměťové členy. Sekvenční obvod se skládá z kombinační části a paměťové části.

Základem sekvenčních obvodů jsou klopné obvody, ze kterých se konstruují dále čítače, registry, paměťové obvody apod. Klopné obvody jsou sekvenční logické obvody, které se používají v číslicových počítačích, kde se vyskytuje potřeba uchovat na určitou dobu signál s logickou hodnotou 0 nebo 1 (neboli obvody s pamětí 1 bit).

Klopný obvod RS z hradel NOR:

1) Stav vstupů R = 1 a S = 0:

- z pravdivostní tabulky členu NOR vyplývá, že má na výstupu logickou 1 jen v případě, kdy oba vstupy jsou 0

- tato podmínka není splněna u horního členu NOR, neboť vstup R = 1 a proto musí být jeho výstup Q = 0

- tato logická 0 se dostane zpětnou vazbou na vstup dolního členu NOR a ten vytvoří na svém výstupu Q = 1

- zpětná vazba na horní člen NOR jeho výstup nezmění

- tím je jednoznačně dán výstup klopného obvodu Q = 0 a Q = 1

- tomuto stavu říkáme RESET = vynulování, protože hlavní výstup Q je v logické 0

2) Stav vstupů R = 0, S = 1

- bude i výstup opačný to je Q = 1 a Q = 0

- tomuto stavu říkáme SET = nastavení, protože obvod má hlavní výstup Q = 1

U obvodu RS nesmí být R = S = 1. To je tzv. nedefinovaný (zakázaný stav). Animaci tohoto klopného obvodu spustíme kliknutím na nadpis "Klopný obvod RS".

Princip dvojčinného JK klopného obvodu umožňuje definovat logickou funkci i pro případ, že oba vstupy jsou ve stavu logická 1. Tento typ obvodu bývá spouštěn týlem taktovacího impulsu. Zapojení obvodu ukazuje následující obrázek.

Obvod má opět oddělené taktovací vstupy obou stupňů klopných obvodů pomocí

invertoru. Zapojením zpětné vazby z výstupu Q na vstup K a z výstupu Q na vstup J se docílí toho, že vstupní kombinaci J = l a K = l na

vstupech obvodu odpovídá překlopení výstupního obvodu do opačného stavu, než byl před příchodem týlu taktovacího impulsu.

Klopný obvod JK je zabezpečen proti vzniku zakázaného stavu na výstupu. Zabezpečení v tomto obvodu pro J = K = 1 snadno odvodíme, víme-li, že na vstupu jsou součinové

členy. Alespoň jeden z nich má totiž na vstupu logickou 0 zavedenou z výstupu, a proto na vstupech R, S prvního RST klopného obvodu nikdy nenastane současně kombinace

dvou jedniček.

Klopné obvody JK jsou vyráběny jako integrované obvody pod označením 7470, 7472 a 7473, které se liší především počtem J a K vstupů, případně dodatečnými nastavovacími

a nulovacími vstupy. Obvody CMOS zastupuje 4027 - dvojitý Master-Slave J-K Flip-Flop.

Animaci lze spustit klepnutím na nadpis. K.O. reaguje na sestupnou hranu hodinového impulsu.

Pravdivostní tabulka obvodu JK

V tab. je znázorněna pravdivostní tabulka JK klopného obvodu a na dalším obr. je uveden jeho diagram přechodů. JK a D klopné obvody jsou významnými pro konstrukci sekvenčních logických obvodů a jako stavební blok integrovaných obvodů.

Tento obvod odstraňuje zakázaný stav propojením obou vstupů klopného obvodu typu RS invertorem. Obvod je řízen (synchronizován) hodinovým vstupem.

Činnost:

- klopný obvod překlápí jen během hodinového impulzu, jinak je zavřený

- invertor zajišťuje, že vstupy do původního klopného obvodu RS mohou být pouze rozdílné (je-li R = 1, pak S = 0 a naopak), neboli obvod pracuje pouze dle druhého a

třetího řádku pravdivostní tabulky klopného obvodu RS

- touto úpravou má obvod pouze jeden vstup

- výstup klopného obvodu typu D kopíruje vstup a uchovává poslední hodnotu výstupu až do další změny vstupu C.

- obvod má paměť o velikosti jednoho bitu a využívá se proto v paměťových registrech

Tento K.O. se vyrábí jako integrovaný obvod 7474 nebo CMOS 4013. Oba obsahují dva klopné obvody typu D. Animaci spustíme klepnutím na nadpis. Informace ze vstupu se zde

kopíruje na výstup pouze při vstupu C v log. jedničce.

Čítačem nazýváme kombinaci klopných obvodů schopnou čítat počet vstupních impulsů a vyjádřit jejich počet pomocí binárního nebo jiného kódu.

Je vyobrazen na obrázku nahoře. Klepnutím na nadpis spustíme animaci, kde je pro jednoduchost znázorněna činnost čítače do čtyř, který by obsahoval pouze dva klopné obvody.

Níže je uveden časový průběh vstupního a výstupních signálů a pravdivostní tabulka. Obojí je pro čítač se čtyřmi klopnými obvody typu T, který čítá do šestnácti. Klopné

obvody T byly vytvořeny pomocí obvodů J-K připojením obou vstupů na log 1. Jednotlivé klopné obvody mění stav výstupu při každé sestupné hraně na hodinovém vstupu (zde je

rozdíl oproti animaci, kde obvod reaguje na náběžnou hranu).

Překlápění se řídí dvěma pravidly:

1. Výstup Q0 obvodu T1 mění svůj stav při každé sestupné hraně vstupních impulsů.

2. Všechny ostatní výstupy mění svůj stav právě když předcházející klopný obvod mění stav výstupu Q z 1 do 0.

Aplikací těchto pravidel dostáváme tvar signálu na výstupech Q0 - Q3 tak jak uvádí obrázek. Vidíme že stav výstupů Q0 - Q3

je binární reprezentace čísla udávajícího pořadí vstupního hodinového impulsu.

Tento čítač se vyrábí jako integrovaný obvod 7493 nebo 4022 z řady 4xxx.

Časový průběh

Pravdivostní tabulka čítače

Synchronní čítače

Z rozboru funkce asynchronních čítačů je zřejmé, že změna stavu z 1 do 0 předcházejícího obvodu teprve působí změnu stavu následujícího obvodu. V případě, že všechny

obvody jsou na logické úrovni 1, vybuzují postupně jeden druhý a doba potřebná k tomu, aby celý čítač vykonal odezvu na vstupní impuls, může být srovnatelná s dobou mezi

jednotlivými impulsy. To je nebezpečné zvláště tehdy, je-li řada obvodů dlouhá, neboť dokud celý řetězec nedosáhne ustáleného stavu, nelze jeho výstupy synchronně (v

jednom okamžiku) odečíst a zařízení tak ztrácí smysl.

Aby se doba odezvy čítače na vstupní impuls snížila, byla opět poněkud modifikována topologie zapojení čítače tak, aby na klopné obvody byl přiveden vstupní impuls

synchronně. V tom případě je však třeba zabezpečit, aby měnily stav jen ty klopné obvody, u kterých je to požadováno. Zde se plně využívá funkce obvodu typu T. Pomocí

řídící logiky se ze stavu výstupů předcházejících obvodů určuje logická úroveň vstupu T a tedy skutečnost, zda klopný obvod změní nebo nezmění stav při aplikaci následného

hodinového impulsu. Čítač se tak v době mezi impulsy “připravuje” na zpracování následného hodinového impulsu. Příklad binárního synchronního čítače je na obr. Použitím

tohoto zapojení lze zhruba zdvojnásobit pracovní frekvenci čítače ve srovnání s asynchronním. Využitím asynchronních vstupů klopných obvodů lze před započetím čítání

nastavit počáteční stav čítače, tj. provést předvolbu.